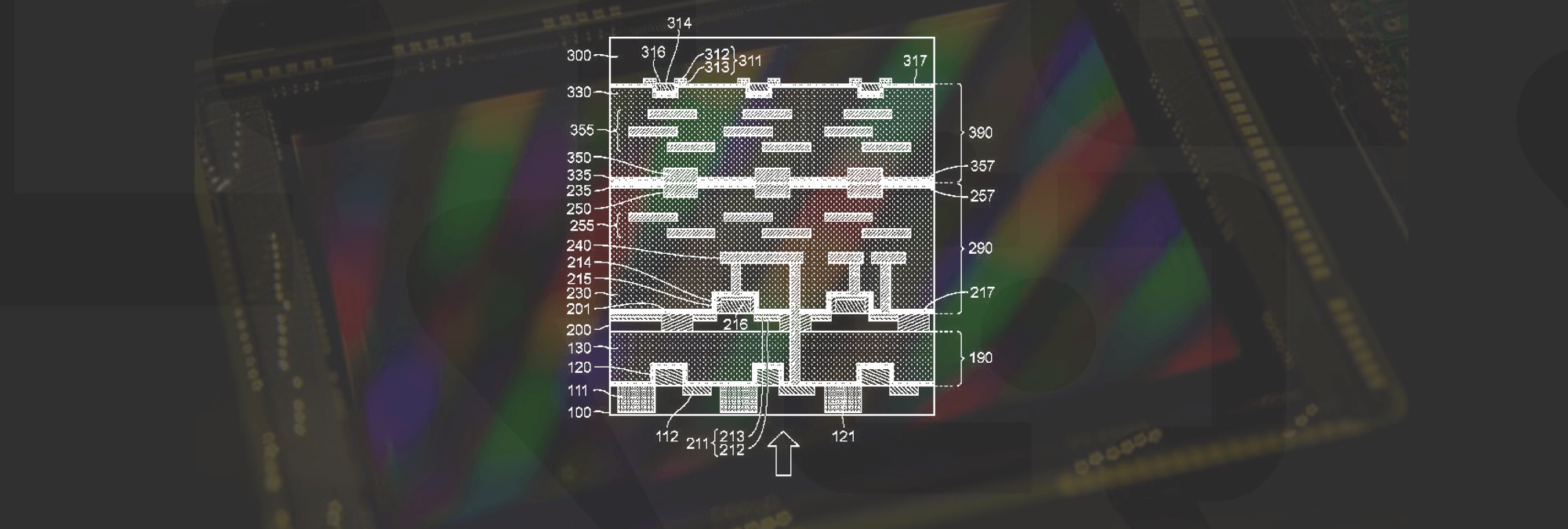

In this patent application (2024-019961) Canon shows off a high-speed stacked sensor using three substrate layers.

As you can imagine, sensor layers are like a house, the more floors you have the more flexibility you have, and the more room. However the cost of manufacturing a house with more and more floors increases as the time required increases, and it gets more expensive from the construction and engineering perspective. Sensors aren’t much different. The more substrates you stack, the greater the chance imperfections are ruining the sensor, the longer it takes to manufacture, and overall a dramatic increase to the engineering challenges.

So Canon for the most part has settled for now on a 2-layer stacked sensor. But for performance reasons, Canon is looking to create 3-layer stacked sensor. In their own words;

To provide a photoelectric conversion device that can be driven at high speed. A first semiconductor layer includes a first member having a photoelectric conversion section and a transfer transistor that transfers charges generated in the photoelectric conversion section. The second semiconductor layer includes a second member having a readout circuit that outputs a signal based on the charge transferred from the transfer transistor. The third semiconductor layer includes a third member having a signal processing circuit that processes signals. A first member, a second member, and a third member are stacked, and a salicide structure is provided in a source region or a drain region of a transistor that constitutes a readout circuit.

Yeah, I hardly understood that either. Basically what we have here is, the top layer is the photodiodes and transfer switch transistor. The second layer is the ADC readout circuitry. The third layer is for further signal processing (things like noise reduction, hdr, and auto-focus processing could be included in this). But patents are not meant to be clear so there you have it.

What Canon is hoping to do with this patent application is lower the source and drain resistance of the transistors on each photodiode. A little electronic basics, on a FET (field effect transistor) there are three terminals called the Gate, Source, and Drain. The terminals are pretty self-explanatory – as the gate controls if the transistor will block or allow current to pass through the source to the drain. Controlling the overall FET resistance atypically allows for faster FETs and also less heat with the same amount of current (heat generated is a function of resistance and current). A prior patent application that Canon talks about reduces the gate resistance – which is a function of the speed of the switch, this patent application deals with the resistance of the source to drain, the other component to making sure a high-resolution sensor can run as fast as possible, without turning into a hotplate.

The faster the transistor on each photodiode can switch the faster the entire sensor will be able to be read. The faster the overall sensor readout speed is then the lower rolling shutter distortion the sensor can exhibit. So all good things here. We do know an R1 is coming. A high-speed sensor would be exactly with this behemoth needs to be the one camera to rule them all.

As with most patent applications, this is a look into Canon’s research, and the more we see about some advanced sensor designs the better.

Source: Japan Patent Application 2024-019961

|

When you purchase through links on our site, we may earn an affiliate commission. Here's how it works. |

I mean First to the Tripple Stack!

1) only more speed (improved FPS, rolling shutter etc.),

2) only more image quality (16 bit RAW files at a decent speed) or

3) both?

Thanks.